RS Flip Flop

UN Ciabatte infradito è un dispositivo bi-stabile. Ci sono tre classi di infradito che sono conosciute come Chiusure, pulse-triggered ciabatte infradito, Edge-triggered ciabatte infradito. In questa parola impostata significa che l'uscita del circuito è uguale a 1 e la parola reset significa che l'uscita è 0. Ci sono due tipi di flip flop uno è un RS Flip Flop e JK Flip Flop. In questo articolo RS Flip Flop è spiegato in dettaglio.

Contenuto:

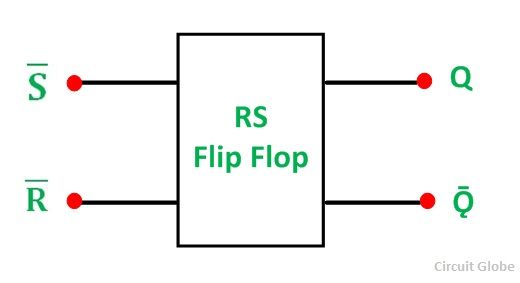

L'RS Flip Flop è considerato uno dei circuiti logici sequenziali più elementari. Il flip flop è un dispositivo bi-stabile di memoria a un bit. Ha due ingressi, uno è chiamato "IMPOSTATO" che imposterà il dispositivo (uscita = 1) ed è etichettato S e un altro è noto come "RESET" che resetterà il dispositivo (uscita = 0) etichettato come R. La sigla RS sta per SET / RESET.

Il flip-flop viene riportato al suo stato originalecon l'aiuto dell'ingresso RESET e l'uscita Q che sarà a livello logico "1" o logica "0". Dipende dalla condizione di set / reset del flip-flop. La parola flip flop significa che può essere “FLIPPED” in uno stato logico o “Floppato” di nuovo in un altro

Viene utilizzato il circuito basculante RS Flip Flop di baseper memorizzare i dati e quindi fornisce il feedback da entrambe le sue uscite di nuovo ai suoi ingressi. L'RS Flip Flop ha in realtà tre ingressi, SET, RESET e la sua uscita corrente Q relativa al suo stato attuale.

Il simbolo del Flip-Flop RS è mostrato sotto.

Flip Flop della porta NAND RS

Una coppia di porte NAND incrociate a 2 unità è lamodo più semplice per rendere qualsiasi basic set / reset a un bit RS Flip Flop. Forma Set / Reset bistabile o un latch di gate LOW RS NAND attivo. Il feedback viene alimentato da ciascuna uscita a uno degli altri ingressi della porta NAND.

Il dispositivo è composto da due ingressi; uno è noto come SET, (S) e l'altro è chiamato RESET, (R). Le due uscite sono Q e Q come mostrato nella figura sotto.

Lo stato impostato

Considerando il circuito sopra. Se l'ingresso R è a livello logico "0" (R = 0) e l'ingresso S è sulla logica "1" (S = 1), la porta NAND Y ha almeno uno dei suoi ingressi in una logica "0 ”. Pertanto, l'uscita Q deve essere a livello logico "1" (principi di porta NAND). L'uscita (Q) viene riportata all'ingresso "A". Entrambi gli ingressi delle porte NAND X sono a "1" logico e, pertanto, l'uscita Q deve essere al livello logico "0".

L'ingresso di reset R modifica il suo stato e vaHIGH to logic "1" con S costante alla logica "1". L'ingresso Y della porta NAND è ora (R = 1) e (B = 0). L'uscita su Q rimane su HIGH o a livello logico "1" in quanto uno dei suoi ingressi è ancora a livello logico "0". Di conseguenza, non vi è alcun cambiamento di stato. Pertanto, il circuito flip-flop è detto "LATCHED" o "SET" con Q = 1 e Ǭ = 0.

Lo stato di reset

In questo secondo stato stabile, Q è a livello logico'0 "e la sua uscita inversa Q è al livello logico" 1 ". Ed è dato da (R = 1) e (S = 0). Poiché il gate X ha uno dei suoi ingressi con uno "0" logico, l'uscita Q deve essere uguale al livello logico "1". (Secondo il principio della porta NAND). L'uscita Q viene inviata all'ingresso B, quindi entrambi gli ingressi alla porta NAND Y sono a "1" logico., Pertanto, Q = 0.

Se l'ingresso impostato S ora cambia lo stato in logica"1" con l'ingresso R rimanente alla logica "1", l'uscita Q rimane BASSA a livello logico "0". E non c'è alcun cambiamento nello stato. Pertanto, lo stato "RESET" dei circuiti flip-flop è stato bloccato.

Il tavolo della verità del Set / Reset è indicato di seguito.

| Stato | S | R | Q | Ǭ | Descrizione |

|---|---|---|---|---|---|

| IMPOSTATO | 1 | 0 | 1 | 0 | Imposta Q >> 1 |

| 1 | 1 | 1 | 0 | Nessun cambiamento | |

| RESET | 0 | 1 | 0 | 1 | Reimposta Q >> 0 |

| 1 | 1 | 0 | 1 | Nessun cambiamento | |

| NON VALIDO | 0 | 0 | 0 | 1 | Memoria con Q = 0 |

| 0 | 0 | 1 | 0 | Memoria con Q = 1 |

Dal tavolo della verità, è chiaro che quando entrambigli ingressi S = 1 e R = 1 le uscite Q e Ǭ possono essere a livello logico '1' o "0" a seconda dello stato degli ingressi. Quando lo stato dell'ingresso R = 0 e S = 0 è una condizione non valida e deve essere evitata perché questo darà entrambe le uscite Q e Ǭ a livello logico "1" allo stesso tempo e la condizione necessaria è che Q sia l'inverso di Ǭ.

Il flip-flop va ad uno stato instabile come entrambil'uscita diventa BASSA. Questa condizione instabile si verifica quando l'ingresso LOW è commutato su HIGH. Il flip-flop passa a uno stato o l'altro e ogni uscita del flip-flop commuta più velocemente dell'altro. Questa condizione instabile è conosciuta come stato Meta-stabile.

Il bistabile RS flip flop o è attivato o impostatoalla logica "1" applicata al suo ingresso S e disattivata o ripristinata da una logica "1" applicata a R. Il flip-flop RS si dice che sia in una condizione non valida se entrambi gli ingressi di set e reset sono attivati simultaneamente.

Il NOR Gate RS Flip Flop

Lo schema elettrico del flip-flop della porta NOR è mostrato nella figura seguente.

Il tavolo della verità del NOR gate RS Flip Flop è mostrato sotto.

| S | R | Q | Ǭ |

|---|---|---|---|

| 0 | 0 | Nessun cambiamento | Nessun cambiamento |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

Gli ingressi sono attivi HIGH e la condizione non valida esiste quando entrambi i suoi ingressi sono a livello logico '1'.