JK Flip Flop

คน JK Flip Flop เป็นปัดพลิกที่ใช้กันอย่างแพร่หลาย จะถือว่าเป็นวงจร flip-flop สากล การดำเนินการตามลำดับของ JK Flip Flop นั้นเหมือนกับ RS flip-flop เช่นเดียวกัน ตลาดหลักทรัพย์ และ RESET อินพุต ข้อแตกต่างคือ JK Flip Flop ไม่ใช่สถานะอินพุตที่ไม่ถูกต้องของ RS Latch (เมื่อ S และ R ทั้งคู่เป็น 1) ชื่อ JK Flip Flop ถูกเก็บไว้ในชื่อนักประดิษฐ์ของวงจรที่รู้จักกันในชื่อ แจ็คคิลบี้ พื้นฐาน สัญลักษณ์ ของ JK Flip Flop ดังแสดงด้านล่าง

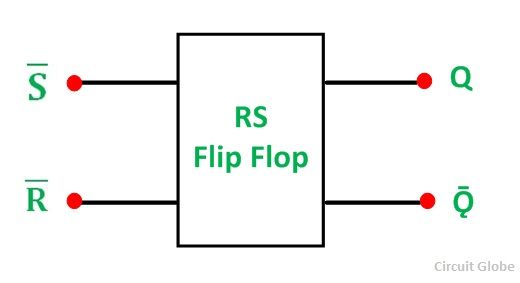

flip-flop NAND gate RS พื้นฐานทนทุกข์ทรมานจากสองปัญหาหลัก ประการแรกควรหลีกเลี่ยงเงื่อนไขเมื่อ S = 0 และ R = 0 ประการที่สองหากสถานะของ S หรือ R เปลี่ยนสถานะในขณะที่อินพุตซึ่งเปิดใช้งานอยู่สูงการกระทำการล็อคที่ถูกต้องจะไม่เกิดขึ้น ดังนั้นเพื่อเอาชนะปัญหาทั้งสองนี้ของ RS Flip-Flop JK Flip Flop จึงได้รับการออกแบบ

JK Flip Flop นั้นเป็น RS flip ที่มีระบบฟลอพด้วยการเพิ่มวงจรอินพุตนาฬิกา เมื่อทั้งอินพุต S และ R เท่ากับตรรกะ“ 1” เงื่อนไขที่ไม่ถูกต้องจะเกิดขึ้น ดังนั้นเพื่อป้องกันสภาพที่ไม่ถูกต้องวงจรนาฬิกาถูกนำมาใช้ JK Flip Flop มีการรวมอินพุตที่เป็นไปได้สี่แบบเนื่องจากมีการเพิ่มอินพุตแบบตอกบัตร อินพุตทั้งสี่คือ“ ลอจิก 1”, ‘ลอจิก 0” "ไม่มีการเปลี่ยนแปลง" และ "สลับ"

คน แผนภูมิวงจรรวม ของ JK Flip Flop ดังแสดงในรูปด้านล่าง

อินพุต S และ R ของ RS bistable ได้รับแล้วแทนที่ด้วยอินพุตทั้งสองที่เรียกว่าอินพุต J และ K ตามลำดับ ที่นี่ J = S และ K = R อินพุตสองและประตูของฟลิปฟล็อปจะถูกแทนที่ด้วยสองอินพุต 3 ประตู NAND ด้วยอินพุตที่สามของแต่ละเกทที่เชื่อมต่อกับเอาต์พุตที่ Q และǬ ครอปเปิลคัปปลิ้งของ RS Flip-Flop นี้ใช้ในการสลับการทำงาน ในฐานะที่เป็นสองอินพุตจะเชื่อมต่อกัน

หากวงจรอยู่ในสภาพ“ SET” แสดงว่า Jอินพุตถูกยับยั้งโดยสถานะ 0 ของ Q ผ่านเกต NAND ด้านล่าง ในทำนองเดียวกันอินพุต K ถูกยับยั้งโดยสถานะ 0 ของ Q ผ่านเกท NAND ด้านบนในสภาพ“ RESET” เมื่อทั้ง J และ K อยู่ที่ตรรกะ“ 1” การสลับ JK Flip Flop

คน ตารางความจริง ของ JK Flip Flop ดังแสดงด้านล่าง

| J | K | Q | Ǭ | ลักษณะ | |

|---|---|---|---|---|---|

| เช่นเดียวกับ RS Latch | 0 | 0 | 0 | 0 | หน่วยความจำไม่มีการเปลี่ยนแปลง |

| 0 | 0 | 0 | 1 | ||

| 0 | 1 | 1 | 0 | รีเซ็ต Q >> 0 | |

| 0 | 1 | 0 | 1 | ||

| 1 | 0 | 0 | 1 | ตั้งค่า Q >> 1 | |

| 1 | 0 | 1 | 0 | ||

| ข้อศอก | 1 | 1 | 0 | 1 | ข้อศอก |

| 1 | 1 | 1 | 0 |

JK Flip Flop นั้นคล้ายกับ RS flip flop ด้วยข้อเสนอแนะซึ่งช่วยให้เพียงหนึ่งในขั้วอินพุตของมัน มันกำจัดสภาพที่ไม่ถูกต้องซึ่งเกิดขึ้นในฟลิปฟล็อปฟล็อปและวางเทอร์มินัลอินพุตเพื่อตั้งค่าหรือรีเซ็ตเงื่อนไขทีละรายการ

เมื่อทั้งอินพุต J และ K อยู่ที่ตรรกะ“ 1” ที่ในเวลาเดียวกันและสัญญาณนาฬิกาเป็นพัลส์ HIGH วงจรจะสลับจากสถานะ SET ไปเป็น RESET หรือกลอนวีซ่า เมื่อเทอร์มินัลทั้งสองเป็น HIGH ฟลิปฟล็อป JK จะทำหน้าที่เป็นตัวสลับ T ประเภทฟล็อป

JK flip-flop มีข้อเสียเปรียบของปัญหาเวลาที่รู้จักกันในชื่อ "แข่ง". เงื่อนไขของ RACE จะเกิดขึ้นหากเอาต์พุต Qเปลี่ยนสถานะก่อนที่จังหวะการจับเวลาของอินพุตนาฬิกามีเวลาที่จะเข้าสู่สถานะปิด ควรกำหนดระยะเวลาการเต้นของชีพจร (T) ให้สั้นที่สุดเท่าที่จะทำได้เพื่อหลีกเลี่ยงปัญหาเรื่องเวลา

เงื่อนไขนี้เป็นไปไม่ได้เสมอดังนั้นชื่อฟลิปฟล็อปที่ได้รับการปรับปรุงให้ดีขึ้นมาก Master Salve JK Flip Flop ได้รับการพัฒนา สิ่งนี้จะช่วยขจัดปัญหาเรื่องเวลาทั้งหมดโดยใช้ RS-flip-flop ที่เชื่อมต่อเป็นอนุกรม หนึ่งสำหรับ “ ปรมาจารย์” วงจรซึ่งทริกเกอร์ที่ขอบนำของพัลส์นาฬิกา ส่วนอีกอันเรียกว่า "ทาส" วงจรซึ่งก่อให้เกิดเมื่อพัลส์นาฬิกาอยู่ที่ขอบตก