RS Flip Flop

A Flip Flop ir divstabila ierīce. Pastāv trīs flip flops klases, ko tās sauc par Slēdzenes, impulsu iedarbināšana flip-flop, Apgrieztā mala flip flop. Šajā komplektā vārds nozīmē, ka ķēdes izvade ir vienāda ar 1, un vārds reset nozīmē, ka izeja ir 0. Ir divi flip flop veidi: RS Flip Flop un JK Flip Flop. Šajā rakstā detalizēti izskaidrots RS Flip Flop.

Saturs:

RS Flip Flop tiek uzskatīts par vienu no visvienkāršākajām secīgajām loģiskajām ķēdēm. Flip Flop ir viena bitu atmiņas stabila ierīce. Tam ir divas ievades, viena tiek saukta “SET” kas iestatīs ierīci (izeja = 1) un ir apzīmēta ar S, bet otrs ir pazīstams kā “RESET” kas atiestatīs ierīci (izejas = 0), kas apzīmēta kā R. RS nozīmē SET / RESET.

Flip-flop tiek atiestatīts atpakaļ uz sākotnējo stāvokliar RESET ievadi un izejas signāls ir Q, kas būs vai nu loģikas līmenī "1", vai loģikā "0". Tas ir atkarīgs no flip-flop iestatītā / atiestatītā stāvokļa. Flip flop vārds nozīmē, ka tas var būt “FLIPPED” vienā loģiskā stāvoklī vai “FLOPPED” atpakaļ citā.

Tiek izmantota pamata NAND vārtu RS Flip Flop ķēdeuzglabāt datus un tādējādi atkal atgriezties no abiem rezultātiem no saviem ieguldījumiem. RS Flip Flop faktiski ir trīs ieejas, SET, RESET un tā pašreizējā izejas Q, kas attiecas uz tās pašreizējo stāvokli.

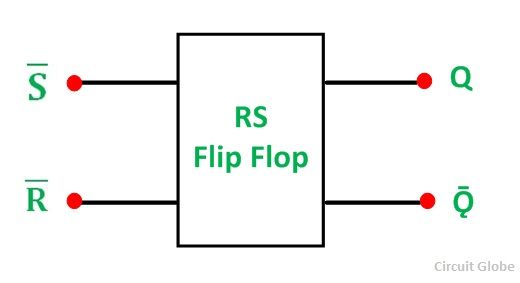

RS Flip-Flop simbols ir parādīts zemāk.

NAND vārti RS Flip Flop

Pāris savienots 2 vienību NAND vārti irvienkāršākais veids, kā padarīt jebkuru pamata bitu komplektu / atiestatīšanu RS Flip Flop. Tā veido Set / Reset bi-stabilu vai aktīvu LOW RS NAND vārtu aizbīdni. Atsauksmes tiek ievadītas no katra izejas uz citu NAND vārtu ieeju.

Ierīce sastāv no divām ieejām; vienu sauc par SET, (S), bet otru sauc par RESET (R). Abi izejas ir Q un Q josla, kā parādīts attēlā.

Iestatīt valsti

Ņemot vērā iepriekš minēto shēmu. Ja ieeja R ir loģiskā līmenī “0” (R = 0) un ievade S ir loģikā “1” (S = 1), tad NAND vārtiem Y ir vismaz viens no tās ievadiem loģikā “0 ”. Tāpēc tā izejai Q jābūt loģiskā līmenī “1” (NAND vārti). Izeja (Q) tiek ievadīta atpakaļ ieejai “A”. Gan NAND vārtu X ieejas ir loģiski “1”, tāpēc tā izejai Q jābūt loģiskā līmenī “0”.

Reset ievads R maina savu stāvokli un ietAUGSTS līdz loģikai “1” ar S konstanti loģikā “1”. Tagad NAND vārtu Y ievade ir (R = 1) un (B = 0). Q izejas vērtība saglabājas augstā līmenī vai loģikas līmenī “1”, jo viens no tā ievadiem joprojām ir loģiskā līmenī “0”. Rezultātā valsts nemainās. Tāpēc tiek uzskatīts, ka flip-flop ķēde ir “LATCHED” vai “SET” ar Q = 1 un Ǭ = 0.

Atjaunot stāvokli

Šajā otrajā stabilajā stāvoklī Q ir loģiskā līmenī“0” un tā apgrieztā jauda Q ir loģiskā līmenī “1”. Un to norāda (R = 1) un (S = 0). Tā kā X vārtiem ir viens no tās ievadiem ar loģiku “0”, tā izejai Q ir jābūt vienādam ar loģiku “1”. (Saskaņā ar NAND vārtu principu). Izeja Q tiek ievadīta B ieejai, tāpēc abi ieejas NAND vārtiem Y ir loģiski “1”, tāpēc Q = 0.

Ja iestatītā ievade S tagad maina stāvokli uz loģiku“1”, kad ieeja R paliek loģikā “1”, izejas Q joprojām ir LOW pie loģiskā līmeņa “0”. Un valstī nav pārmaiņu. Tāpēc ir bloķētas flip-flop shēmas “RESET”.

The patiesības tabula no Set / Reset ir norādīts zemāk.

| Valsts | S | R | Q | Ǭ | Apraksts |

|---|---|---|---|---|---|

| SET | 1 | 0 | 1 | 0 | Iestatīt Q >> 1 |

| 1 | 1 | 1 | 0 | Bez izmaiņām | |

| RESET | 0 | 1 | 0 | 1 | Atiestatīt Q >> 0 |

| 1 | 1 | 0 | 1 | Bez izmaiņām | |

| NEPIECIEŠAMS | 0 | 0 | 0 | 1 | Atmiņa ar Q = 0 |

| 0 | 0 | 1 | 0 | Atmiņa ar Q = 1 |

No patiesības tabulas ir skaidrs, ka tad, kad abiIeejas S = 1 un R = 1 izejas Q un Ǭ var būt vai nu loģiskā līmenī “1” vai “0” atkarībā no ieeju stāvokļa. Ja ieejas stāvoklis R = 0 un S = 0 ir nederīgs stāvoklis, un tas ir jāizvairās, jo tas vienlaikus dos abiem izejas Q un ic loģikas līmenim “1” un nepieciešamais nosacījums ir, ka Q ir apgriezts Ǭ.

Flip-flop iet uz nestabilu stāvokli kā abiemizeja notiek zemāk. Šis nestabils stāvoklis rodas, kad LOW ievade tiek pārslēgta uz HIGH. Flip-flop pārslēdzas uz vienu valsti vai otru, un jebkurš flip-flop izeja tiek pārslēgta ātrāk nekā otrs. Šo nestabilo stāvokli sauc par Meta-stabilu stāvokli.

Bistable RS flip flop vai ir aktivizēts vai iestatītspie loģikas “1”, ko piemēro savai S ievadei un deaktivizē vai atiestata ar loģiku “1”, ko piemēro R. RS flip-flop tiek uzskatīts par nederīgu, ja gan iestatītie, gan atiestatītie ievades tiek aktivizēti vienlaicīgi.

NOR Gate RS Flip Flop

NOR vārtu flip-flop shēma ir parādīta attēlā.

The patiesības tabula no NOR vārti RS Flip Flop ir parādīts zemāk.

| S | R | Q | Ǭ |

|---|---|---|---|

| 0 | 0 | Bez izmaiņām | Bez izmaiņām |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

Ieejas ir aktīvas HIGH un nederīgs nosacījums pastāv, ja abas tās ieejas ir loģiskā līmenī “1”.